SLIDE 1

1

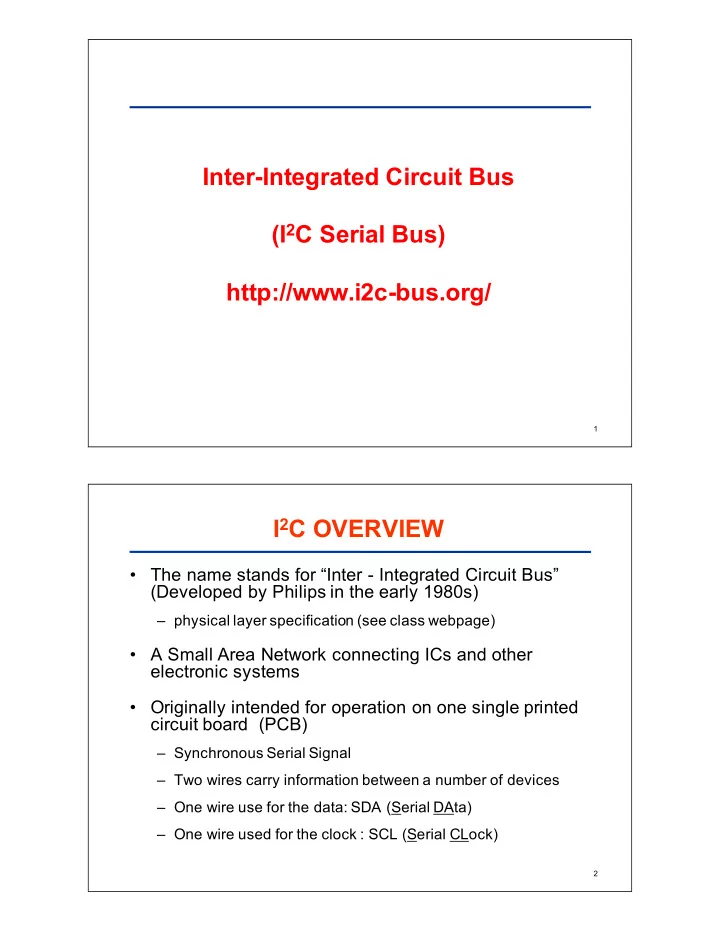

Inter&Integrated*Circuit*Bus (I2C*Serial*Bus) http://www.i2c&bus.org/

2

I2C*OVERVIEW

- The'name'stands'for'“Inter'3 Integrated'Circuit'Bus”'

(Developed'by'Philips'in'the'early'1980s)

– physical'layer'specification'(see'class'webpage)

- A'Small'Area'Network'connecting'ICs'and'other'

electronic'systems

- Originally'intended'for'operation'on'one'single'printed'