1

Input/Output Organization

Chapter 19

- S. Dandamudi

2003

To be used with S. Dandamudi, “Fundamentals of Computer Organization and Design,” Springer, 2003.

S. Dandamudi Chapter 19: Page 2

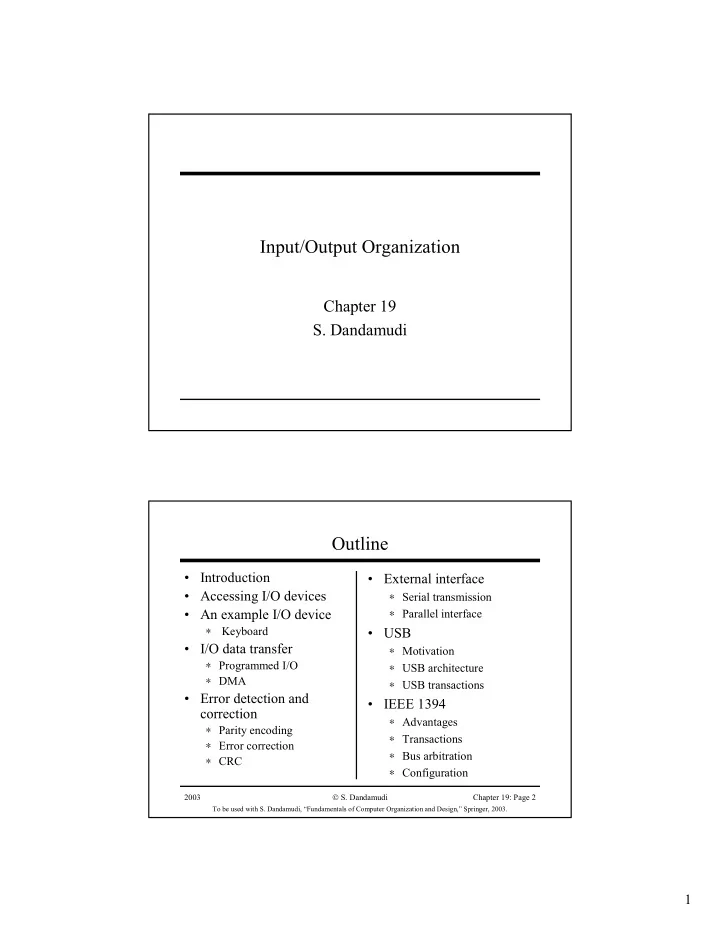

Outline

- Introduction

- Accessing I/O devices

- An example I/O device

∗ Keyboard

- I/O data transfer

∗ Programmed I/O ∗ DMA

- Error detection and

correction

∗ Parity encoding ∗ Error correction ∗ CRC

- External interface

∗ Serial transmission ∗ Parallel interface

- USB

∗ Motivation ∗ USB architecture ∗ USB transactions

- IEEE 1394