FSM$Modeling

- State$Diagrams$(SDs)$and$Algorithmic$State$

Machine$(ASM)$charts$Describe$Behavior$of$FSMs

- Translating$Directly$from$SD/ASMs$to$Verilog$is$

Advantageous

– No$Worry$about$Mistake$in$Logic$Simplification – No$Tedious$Tables$to$Create – Automatic$Tools$(synthesis)$Create$the$Schematic$ Directly – Synthesis$Tools$can$Handle$Very$Large$FSMs$(100s$ even$1000s$of$DFFs) – Can$EASILY$Change$State$Assignment

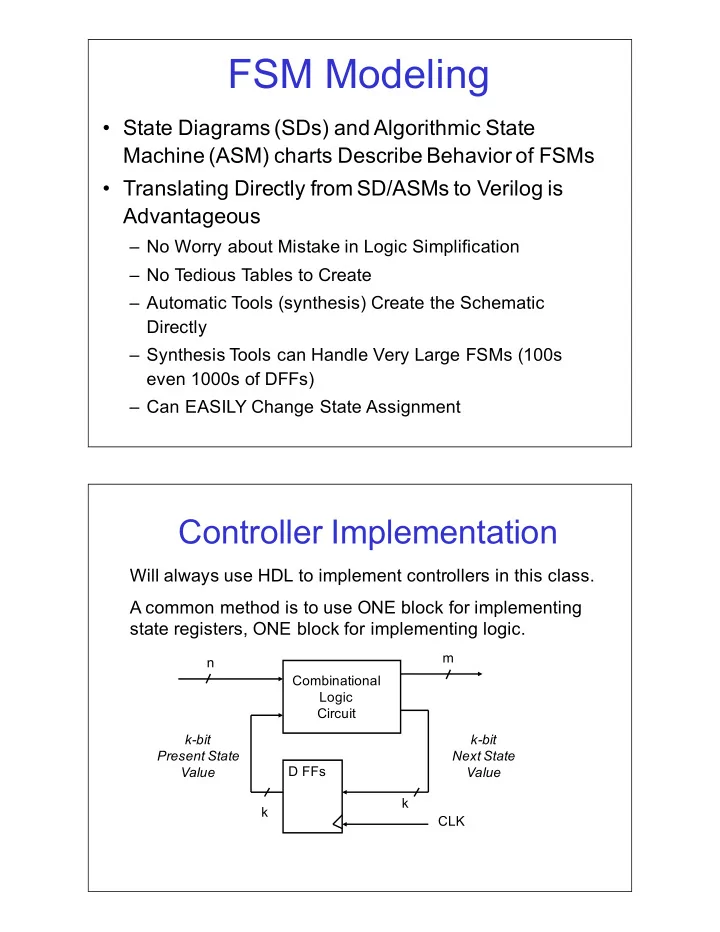

Controller$Implementation

Will$always$use$HDL$to$implement$controllers$in$this$class. A$common$method$is$to$use$ONE$block$for$implementing$ state$registers,$ONE$block$for$implementing$logic.

Combinational Logic Circuit D$FFs n m k k k"bit Present+State Value k"bit Next+State Value CLK