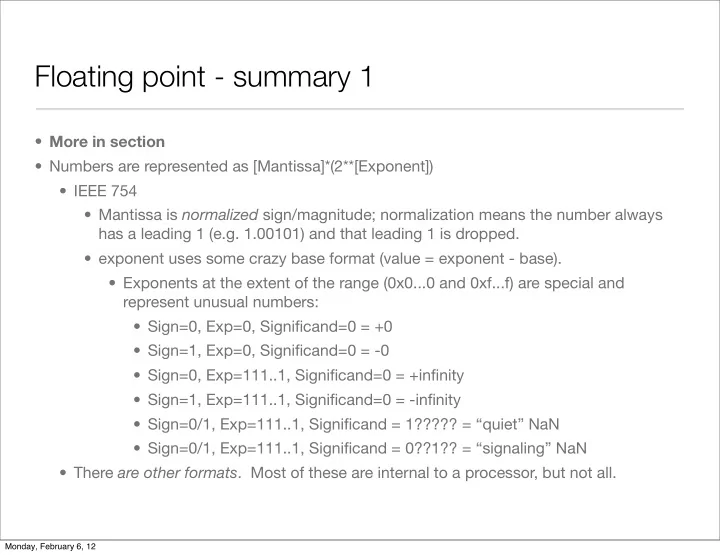

Floating point - summary 1

- More in section

- Numbers are represented as [Mantissa]*(2**[Exponent])

- IEEE 754

- Mantissa is normalized sign/magnitude; normalization means the number always

has a leading 1 (e.g. 1.00101) and that leading 1 is dropped.

- exponent uses some crazy base format (value = exponent - base).

- Exponents at the extent of the range (0x0...0 and 0xf...f) are special and

represent unusual numbers:

- Sign=0, Exp=0, Significand=0 = +0

- Sign=1, Exp=0, Significand=0 = -0

- Sign=0, Exp=111..1, Significand=0 = +infinity

- Sign=1, Exp=111..1, Significand=0 = -infinity

- Sign=0/1, Exp=111..1, Significand = 1????? = “quiet” NaN

- Sign=0/1, Exp=111..1, Significand = 0??1?? = “signaling” NaN

- There are other formats. Most of these are internal to a processor, but not all.

Monday, February 6, 12