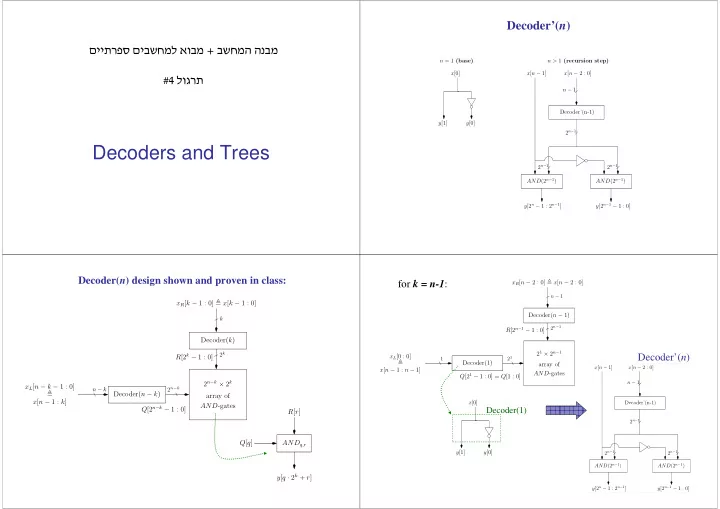

Decoders and Trees

- n > 1 (recursion step)

AND(2n−1) AND(2n−1) 2n−1 2n−1 2n−1 Decoder’(n-1) y[2n − 1 : 2n−1] y[2n−1 − 1 : 0] n − 1 x[n − 2 : 0] x[n − 1] x[0] y[0] y[1] n = 1 (base)

Decoder’(n)

R[2k − 1 : 0] Decoder(n − k) Decoder(k) xL[n − k − 1 : 0] x[n − 1 : k]

- xR[k − 1 : 0] x[k − 1 : 0]

k 2k

2n−k × 2k array of AND-gates Q[2n−k − 1 : 0]

n − k 2n−k

R[r] ANDq,r y[q · 2k + r] Q[q]

Decoder(n) design shown and proven in class:

21 2n−1

xR[n − 2 : 0] x[n − 2 : 0] Decoder(n − 1) Decoder(1) Q[21 − 1 : 0] = Q[1 : 0]

1 n − 1

21 × 2n−1 array of AND-gates xL[0 : 0] x[n − 1 : n − 1]

- R[2n−1 − 1 : 0]

x[n − 1] AND(2n−1) AND(2n−1) 2n−1 2n−1 2n−1 Decoder’(n-1) y[2n − 1 : 2n−1] y[2n−1 − 1 : 0] n − 1 x[n − 2 : 0]

for k = n-1:

y[1] x[0] y[0]

Decoder(1)