CS452/652 Real-Time Programming Course Notes

Daniel M. Berry, Cheriton School of Computer Science University of Waterloo

2007 Daniel M. Berry Real-Time Programming: Trains

- Pg. 1

Documentation Requirements

For the Kernel Assignment: g Description of all major components of the system, e.g. memory management, task management, context switching. Context switching should be described in detail. g Description of kernel data structures and algorithms, e.g., task descriptors, scheduler, etc. g Description of syscall implementation, including parameter passing.

2007 Daniel M. Berry Real-Time Programming: Trains

- Pg. 2

- Doc. Reqs., Cont’d

g Explain why your implementation meets real-time requirements, by giving the complexity of each kernel operation. g Description of test cases, including that they cover what should be tested. g User’s manual g Tour of source code.

2007 Daniel M. Berry Real-Time Programming: Trains

- Pg. 3

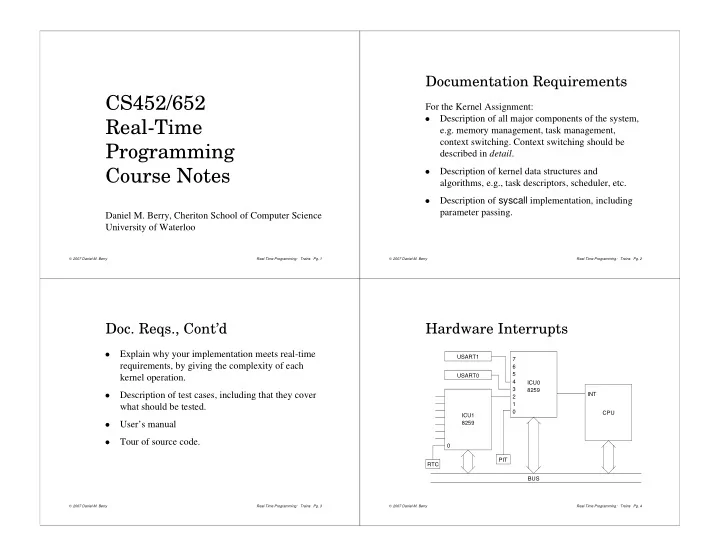

Hardware Interrupts

7 6 5 4 3 2 1 USART1 USART0 ICU1 8259 RTC PIT ICU0 8259 CPU INT BUS

2007 Daniel M. Berry Real-Time Programming: Trains

- Pg. 4