CS 126 Lecture A4: Sequential Circuits

CS126 12-1 Randy Wang

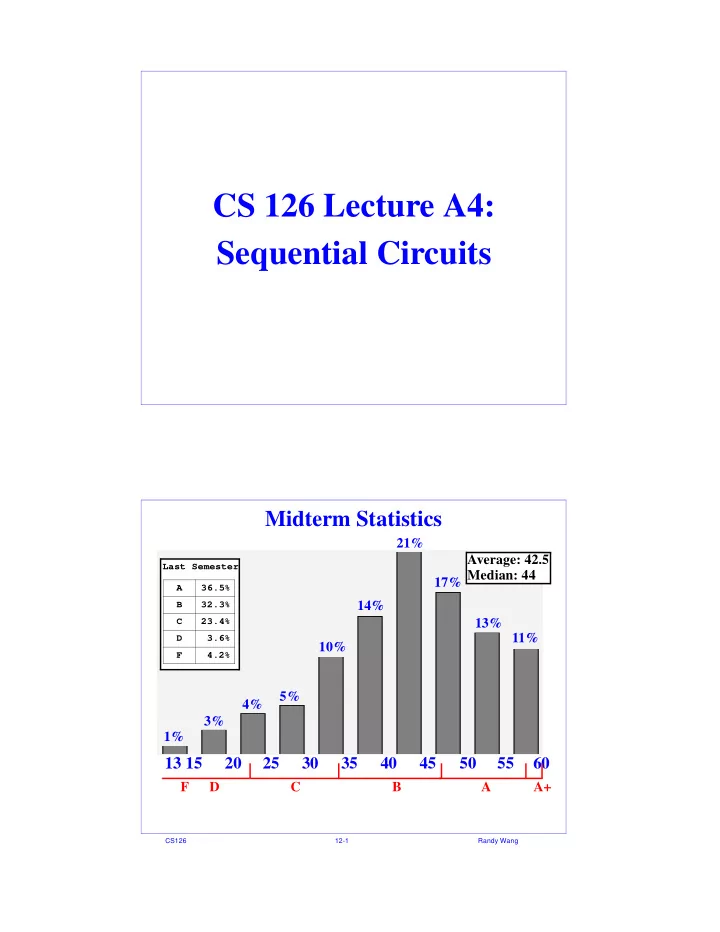

Midterm Statistics

60 55 50 45 40 35 30 25 20 15 13

11% 13% 17% 21% 14% 10% 5% 4% 3% 1% A+ A B C D F Average: 42.5 Median: 44

A 36.5% B 32.3% C 23.4% D 3.6% F 4.2% Last Semester

CS 126 Lecture A4: Sequential Circuits Midterm Statistics 21% - - PDF document

CS 126 Lecture A4: Sequential Circuits Midterm Statistics 21% Average: 42.5 Last Semester Median: 44 17% A 36.5% 14% B 32.3% C 23.4% 13% 11% D 3.6% 10% F 4.2% 5% 4% 3% 1% 13 15 20 25 30 35 40 45 50 55 60 F D C

CS126 12-1 Randy Wang

60 55 50 45 40 35 30 25 20 15 13

11% 13% 17% 21% 14% 10% 5% 4% 3% 1% A+ A B C D F Average: 42.5 Median: 44

A 36.5% B 32.3% C 23.4% D 3.6% F 4.2% Last Semester

CS126 12-2 Randy Wang

CS126 12-3 Randy Wang

machine: the instruction set architecture

interface:

CS126 12-4 Randy Wang

depend on results of previous ones

CS126 12-5 Randy Wang

Circuit x1 x2 xm

I n p u ts

z1 z2 zn

O u tp u ts

Circuit x1 x2

I n p u ts

z1 z2 zn

O u tp u ts

zn-1 Sequential Combinational

Memory

CS126 12-6 Randy Wang

CS126 12-7 Randy Wang

Interface Implementation

CS126 12-8 Randy Wang

diagram is one of the ways of describing them

CS126 12-9 Randy Wang

previous state next state

CS126 12-10 Randy Wang

terms of its present state and inputs (also called next state equations)

important tools for understanding and constructing more sophisticated sequential circuits as well

CS126 12-11 Randy Wang

CS126 12-12 Randy Wang

cycle time rising edge falling edge

CS126 12-13 Randy Wang

interface implementation timing diagram

CS126 12-14 Randy Wang

Interface Implementation

CS126 12-15 Randy Wang

Timing Diagram Truth Table

Q+ = D

Characteristic Equation

CS126 12-16 Randy Wang

edge of a clock signal

sometimes need them to change state on the falling edge

cycle time rising edge falling edge

CS126 12-17 Randy Wang

during the pulse, output changes on falling edge

during clock pulse

Im plem entation

Tim ing D iagram

On rising edge, input copied into master; On falling edge, master copies data into slave.

Cl D Q

Interface

M S

CS126 12-18 Randy Wang

CS126 12-19 Randy Wang

Input Output

CS126 12-20 Randy Wang

C l D Q

x0 y0

C l D Q

x1 y1

C l D Q

xn-1 yn-1 Cl Load

CS126 12-21 Randy Wang

clock pulse

reg 0 reg 1 reg 2 reg n-1

input write Clock

=

address

log2n k

CS126 12-22 Randy Wang

Cl D

y0

Cl D

y1

Cl D

yn-1

address

Decoder

in w Cl

Multiplexer

CS126 12-23 Randy Wang

Cl D Cl D Cl D Cl D

No Yes

CS126 12-24 Randy Wang

Cl D

y0

Cl D

y1

Cl D

yn-1

address

Decoder

in w Cl

CS126 12-25 Randy Wang

case

reg 0 reg 1 reg 2 reg n-1

input write Clock

address

log2n

k k

CS126 12-26 Randy Wang

Multiplexer Multiplexer Multiplexer

y0

Cl D

y1

Cl D

yn-1

address

Decoder

in w Cl

Multiplexer

Cl D

number of registers (n) n u m b e r

b i t s p e r r e g i s t e r ( k )

CS126 12-27 Randy Wang

CS126 12-28 Randy Wang

can’t do this!

CS126 12-29 Randy Wang

register file: no need to replicate decoders for each bit

bits words don’t need decoder if already has decoder inside each bit

CS126 12-30 Randy Wang

CS126 12-31 Randy Wang

cycle is twice as long as the input clock

Cl D Q Cl Q

interface implementation timing diagram

CS126 12-32 Randy Wang

to an (n-1) bit counter

Cl

interface

C l Q 0 C l Q 1 C l Q n -1

im p lem entation Q 0 Q 1 Q 2

Tim ing D iagram

CS126 12-33 Randy Wang

CS126 12-34 Randy Wang

changes to make in response to inputs and past history

“Memory” “Control” “Data”

CS126 12-35 Randy Wang

edge triggered])

equations)