1

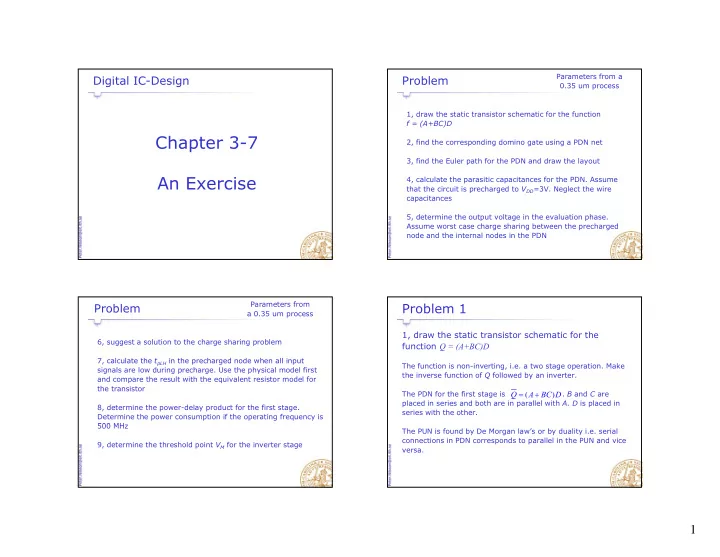

Digital IC-Design

Chapter 3-7 An Exercise

1, draw the static transistor schematic for the function f = (A+BC)D

Problem

Parameters from a 0.35 um process 2, find the corresponding domino gate using a PDN net 3, find the Euler path for the PDN and draw the layout 4, calculate the parasitic capacitances for the PDN. Assume that the circuit is precharged to VDD=3V. Neglect the wire it capacitances 5, determine the output voltage in the evaluation phase. Assume worst case charge sharing between the precharged node and the internal nodes in the PDN 6, suggest a solution to the charge sharing problem 7 calculate the t in the precharged node when all input

Problem

Parameters from a 0.35 um process 7, calculate the tpLH in the precharged node when all input signals are low during precharge. Use the physical model first and compare the result with the equivalent resistor model for the transistor 8, determine the power-delay product for the first stage. Determine the power consumption if the operating frequency is 500 MH 500 MHz 9, determine the threshold point VM for the inverter stage

1, draw the static transistor schematic for the function Q = (A+BC)D

Problem 1

The function is non-inverting, i.e. a two stage operation. Make the inverse function of Q followed by an inverter. The PDN for the first stage is . B and C are placed in series and both are in parallel with A. D is placed in series with the other.

( ) Q A BC D = +

The PUN is found by De Morgan law’s or by duality i.e. serial connections in PDN corresponds to parallel in the PUN and vice versa.