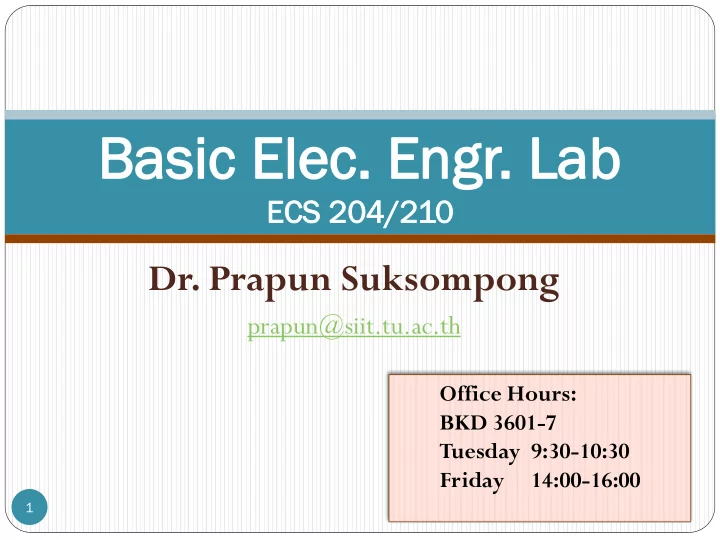

- Dr. Prapun Suksompong

prapun@siit.tu.ac.th

1

Bas Basic ic El Elec.

- ec. En

Engr gr. . Lab Lab

EC ECS S 204 04/210

Office Hours: BKD 3601-7 Tuesday 9:30-10:30 Friday 14:00-16:00

Bas Basic ic El Elec. ec. En Engr gr. . Lab Lab ECS EC S - - PowerPoint PPT Presentation

Bas Basic ic El Elec. ec. En Engr gr. . Lab Lab ECS EC S 204 04/210 Dr. Prapun Suksompong prapun@siit.tu.ac.th Office Hours: BKD 3601-7 Tuesday 9:30-10:30 Friday 14:00-16:00 1 Lab 7 Operational amplifier Inverting

prapun@siit.tu.ac.th

1

Office Hours: BKD 3601-7 Tuesday 9:30-10:30 Friday 14:00-16:00

2

Operational amplifier Inverting amplifier Inverting Integrator

3

OPerational AMPlifier

(1) Offset null + (2) Inverting input (3) Noninverting input (4) V- NC (8) V+ (7) Offset null (5) Output (6) Noninverting input Inverting input V+ , Positive power supply V- , Negative power supply Output (3) (2) (7) (4) (6)

O

4

Plug in op amp chips so that they straddle the troughs on the

proto board.

In this way, each pin is connected to a different hole set.

5

The op amp must be powered by

voltage supplies.

These supplies are often ignored

in op amp circuit diagrams for the sake of simplicity.

Noninverting input Inverting input (3) (2) (7) (4) (6) + Vcc

Vcc

+ (2) Inverting input (3) Noninverting input (4) V- NC (8) V+ (7) Offset null (5) Output (6)

O

6

F

R

R V V. R

RR Vi RF +5 V

+ + Vo

6 4 2 3 Sinusoid 1 kHz

7

F

R

R V V. R

RR Vi RF +5 V

+ Vo 7 6 4 2 3 Sinusoid 1 kHz

+ Vcc

Vcc

CH2

8

9

R + + vo

iin vi V+ V- X C + vC -

Zero-average input (DC offset = 0)

1

i C i

i t i t v t d C v t R dt v t v v t dt RC

h 2 h h 1 2 T h RC

Area = hT/2

T

i

v t

t

10

An input with nonzero mean

(DC offset) can saturate the

R + + vo

iin vi V+ V- X C + vC -

1

i C i

i t i t v t d C v t R dt v t v v t dt RC

T

i

v t

t

11

The gain at f = 0 is unbounded.

R + + vo

iin vi V+ V- X C + vC -

1

C

i

Z V V R V R j C

12

In practical circuit, a large resistor Rp is usually shunted

across the capacitor

Observe that at f = 0, the gain is finite.

R + C + vo

vi V+ V- X Rp

/ / 1

C p

p i p

Z R V V R R V R j R C

13

The output will not be

triangular anymore.

“Virtually triangular” if

RpC >> T/2.

R + C + vo

vi V+ V- X Rp

h 1 1 Rp R r h r

1 2 exp

p

r fR C

i

v t

t