Fachgebiet Rechnersysteme Verification Technology Technische Universität Darmstadt

- 8. Assertion-Based Design and Assertion Languages

1

- 8. Assertion Based Design and

Assertion Languages

Fachgebiet Rechnersysteme Verification Technology

Content

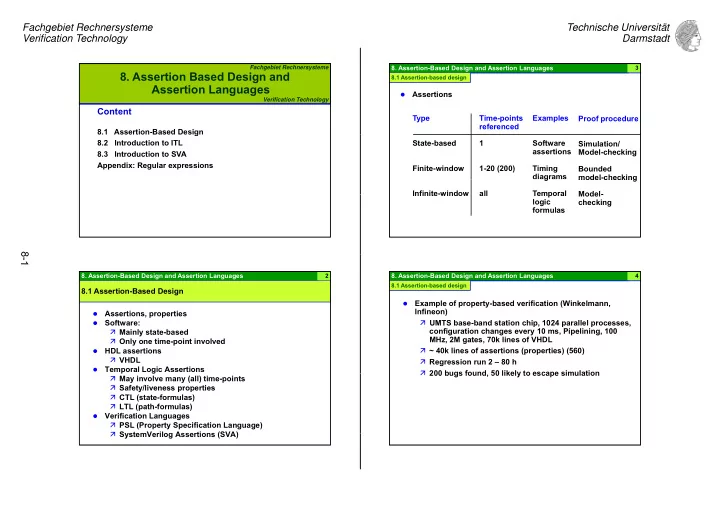

8.1 Assertion-Based Design 8.2 Introduction to ITL 8.3 Introduction to SVA Appendix: Regular expressions

- 8. Assertion-Based Design and Assertion Languages

2

Assertions, properties

Software: 8.1 Assertion-Based Design Mainly state-based Only one time-point involved

HDL assertions VHDL

Temporal Logic Assertions May involve many (all) time-points Safety/liveness properties Safety/liveness properties CTL (state-formulas) LTL (path-formulas)

Verification Languages PSL (Property Specification Language) SystemVerilog Assertions (SVA)

- 8. Assertion-Based Design and Assertion Languages

3 8.1 Assertion-based design

Assertions Type Time-points Proof procedure Examples yp State-based Finite-window p referenced 1 1-20 (200) Proof procedure Simulation/ Model-checking Bounded model-checking p Software assertions Timing diagrams Infinite-window all model checking Model- checking g Temporal logic formulas

- 8. Assertion-Based Design and Assertion Languages

4

Example of property-based verification (Winkelmann, Infineon) UMTS base-band station chip, 1024 parallel processes, fi ti h 10 Pi li i 100

8.1 Assertion-based design