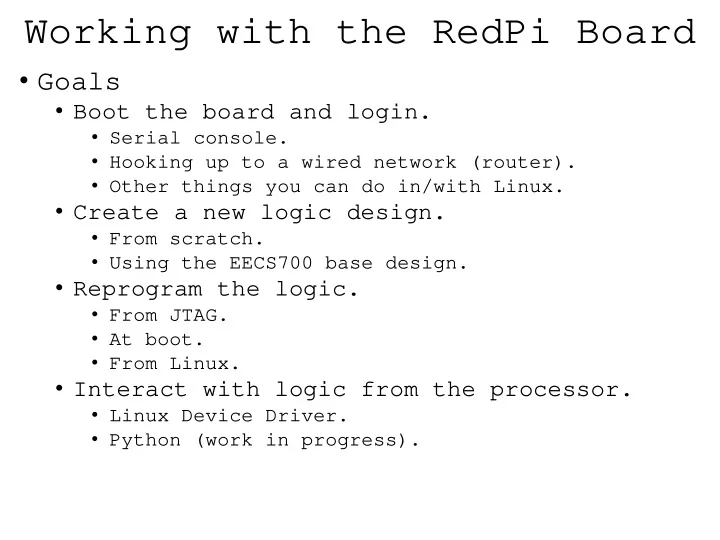

Working with the RedPi Board Goals Boot the board and login. - PowerPoint PPT Presentation

Working with the RedPi Board Goals Boot the board and login. Serial console. Hooking up to a wired network (router). Other things you can do in/with Linux. Create a new logic design. From scratch. Using the EECS700

Working with the RedPi Board • Goals • Boot the board and login. • Serial console. • Hooking up to a wired network (router). • Other things you can do in/with Linux. • Create a new logic design. • From scratch. • Using the EECS700 base design. • Reprogram the logic. • From JTAG. • At boot. • From Linux. • Interact with logic from the processor. • Linux Device Driver. • Python (work in progress).

Boot and Login • With the SD formatted and inserted. • Attach Serial Cable (USB to micro USB) from Host to Console. • Start terminal program (I prefer Tera Term) and make a connection to the correct com port and 115200 baud 8N1. • Attach micro USB power.

Console

Things you can do in Linux • Access the internet via a wired ethernet connection. • Need access to a router.

Options for a wired port. • If you have wifi and don’t have readily available access to a network port. • Forward wifi to ethernet port on you laptop. • Wifi extender with a network port.

Things you can do in Linux • Install software. • apt-get install lrzsz (let’s you do file transfers over the serial connection)

Things you can do in Linux • Transfer a file over serial connection using zmodem. • “rz –be” from command prompt. • File ► Transfer ► ZMODEM ► Send

Things you can do with Linux • Access files remotely ssh server. • WinSCP, Filezilla from host.

Things you can do in Linux • Mount the boot directory.

Logic Design • Understanding the Device UART, LEDs, SD Card, ADC, DAC, Network, IO, ... JTAG USB, RAM ... Data xfer, PL program, Interrupts, Processing Clocks, ... Programmable System (PS) Logic (PL)

Create a new logic design • Open Vivado, Create Project, RTL & don’t specify sources. • The device is xc7z010clg400-1.

Create a new logic design • Add sources, design sources, create file, give it a name, finish, cancel to describing port.

Create a new logic design • Simple Verilog file. • Still need to figure out which pins are connected to LEDs. Some detective work gives us the answer.

Create a new logic design • Add sources, constraints, create ... • Generate bitstream. And wait. • Don’t open implemented design.

Program the device - JTAG • The logic only design does not involve the processing system (PS) so must be programmed via JTAG. • Power off & remove the SD card. • Connect JTAG HS2 Programmer correctly and with strain relief.

Program the device - JTAG • Open hardware manager, connect, program.

EECS700 Base Design • Top level Verilog module and PS block design. • Starting point to incorporate custom peripherals. • Components • Configures the PS for booting Linux. • Accepts interrupts from the PL. • Provides bus access from PS to PL. • Address, Data, Read Strobe, Write Strobe, Handshaking. • 32 bit transfers. • DMA Transfers are capable but not implemented in the class design.

EECS700 Base Design • Top level Verilog file. • Port Description

EECS700 Base Design • Instantiate the PS.

EECS700 Base Design • Description of PL. • Will go into details later. Two Registers: 0x43C0_0000: in/out value 0x43C0_0004: direction

EECS700 Base Design • Standalone Application include ... int main () { ... out32(0x43C00004, 0xFF); out32(0x43C00000, 0xAA); ... }

EECS700 Base Design • Standalone Application include ... if (avb_write) case (avb_address) int main () { (BASE_ADDRESS+0): gp_out <= avb_writedata; ... (BASE_ADDRESS+4): gp_dir <= avb_writedata; out32(0x43C00004, 0xFF); endcase out32(0x43C00000, 0xAA); ... } AVB Bus write address = 0x43C00004 value = 0xFF

EECS700 Base Design • Standalone Application include ... if (avb_write) case (avb_address) int main () { (BASE_ADDRESS+0): gp_out <= avb_writedata; ... (BASE_ADDRESS+4): gp_dir <= avb_writedata; out32(0x43C00004, 0xFF); endcase out32(0x43C00000, 0xAA); ... } AVB Bus write address = 0x43C00000 value = 0xAA

EECS700 Base Design • Standalone Application include ... int main () { ... assign led_o = gpio_out[7:0]; out32(0x43C00004, 0xFF); out32(0x43C00000, 0xAA); ... }

EECS Base Design • Standalone Code

EECS700 Base Design • Building the Base Design. • Download the BaseDesign.zip file from the website and extract. • Start Vivado, but do not open a project (you should be at the start page). • From the tcl console at the bottom of Vivado, cd to the extracted directory and run > source design1.tcl • It should create a new project with all the source files. • You will need to click generate bitstream and wait for it to compile.

EECS700 Base Design

EECS700 Base Design • Compiling the code. • In Vivado: • After bitstream is complete. • File, Export, Export Hardware. • Make sure to check “include bitstream”. • File, Launch SDK.

EECS700 Base Design • Compiling the code. • By starting SDK from within Vivado (and after exporting the hardware) it will automatically build the hardware project in SDK (Just wait for it to finish). • After the hardware project is built SDK should look something like.

EECS700 Base Design • Compiling the code. • In SDK: • File, New, Application Project. • Give it a name and check to make sure the target hardware is correct, Next (not Finish). • Hello World Program, Finish, and wait for everything to compile.

EECS700 Base Design • Modifying Hello World • If you run the program now, it will simply print “Hello World” to the serial port. • Open the code and add modify by adding what is in the red boxes below. • It will automatically compile when you save.

EECS700 Base Design Program the FPGA Click down arrow and run as, Launch on Hardware (System Debugger)

EECS700 Base Design • What does the following do and what does the syntax mean? #define in32(addr) (*(volatile unsigned long *)(addr)) #define out32(addr) (*(volatile unsigned long *)(addr)=(data))

EECS700 Base Design • Interacting with the Base design from Linux rather than standalone. • In Linux, the bit file is renamed logic.bit and copied to the boot partition of the SD card. • Writing to registers is done through low level memory access. • Custom driver • /dev/uio

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![CS 61A Lecture 10 Announcements Lists ['Demo'] Working with Lists 4 Working with Lists](https://c.sambuz.com/1020114/cs-61a-lecture-10-announcements-lists-s.webp)