Introduction to the PS3 Programming the SPEs PS3-clusters Results

Text

1 / 24

Text 1 / 24 Introduction to the PS3 Programming the SPEs - - PowerPoint PPT Presentation

Introduction to the PS3 Programming the SPEs PS3-clusters Results Text 1 / 24 Introduction to the PS3 Programming the SPEs PS3-clusters Results Why is the PlayStation 3 (PS3) hardware of any interest? How should we implement our

Introduction to the PS3 Programming the SPEs PS3-clusters Results

1 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results

2 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Overview Hardware

3 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Overview Hardware

4 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Overview Hardware

5 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Overview Hardware

6 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Overview Hardware

7 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Overview Hardware

7 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Overview Hardware

7 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Overview Hardware

8 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Limitations SIMD Special instructions SPU pipelines

9 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Limitations SIMD Special instructions SPU pipelines

9 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Limitations SIMD Special instructions SPU pipelines

9 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Limitations SIMD Special instructions SPU pipelines

10 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Limitations SIMD Special instructions SPU pipelines

10 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Limitations SIMD Special instructions SPU pipelines

11 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Limitations SIMD Special instructions SPU pipelines

11 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Limitations SIMD Special instructions SPU pipelines

12 / 24

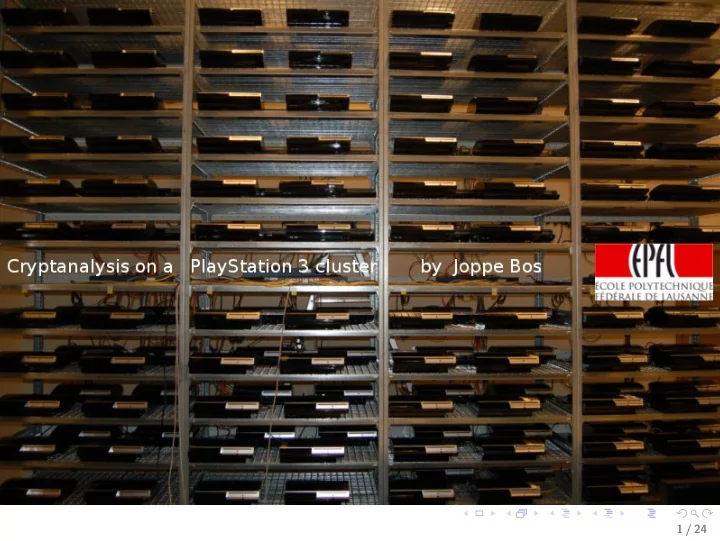

Introduction to the PS3 Programming the SPEs PS3-clusters Results Small clusters Big clusters LACAL PS3 cluster

13 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Small clusters Big clusters LACAL PS3 cluster

13 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Small clusters Big clusters LACAL PS3 cluster

14 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Small clusters Big clusters LACAL PS3 cluster

14 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Small clusters Big clusters LACAL PS3 cluster

15 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Small clusters Big clusters LACAL PS3 cluster

15 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Small clusters Big clusters LACAL PS3 cluster

16 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Small clusters Big clusters LACAL PS3 cluster

17 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Small clusters Big clusters LACAL PS3 cluster

17 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Hashing ECM Pollard rho Future

18 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Hashing ECM Pollard rho Future

19 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Hashing ECM Pollard rho Future

20 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Hashing ECM Pollard rho Future

20 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Hashing ECM Pollard rho Future

20 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Hashing ECM Pollard rho Future

20 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Hashing ECM Pollard rho Future

21 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Hashing ECM Pollard rho Future

22 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Hashing ECM Pollard rho Future

22 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Hashing ECM Pollard rho Future

23 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Hashing ECM Pollard rho Future

24 / 24

Introduction to the PS3 Programming the SPEs PS3-clusters Results Hashing ECM Pollard rho Future

24 / 24