Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se Integer arithmetic

Introduction to Structured VLSI Design ‐ Integer Arithmetic and Pipelining

Joachim Rodrigues

Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se Integer arithmetic

Outline

- Multiplication in the digital domain

- HW‐mapping

- Pipelining optimization

Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se Integer arithmetic

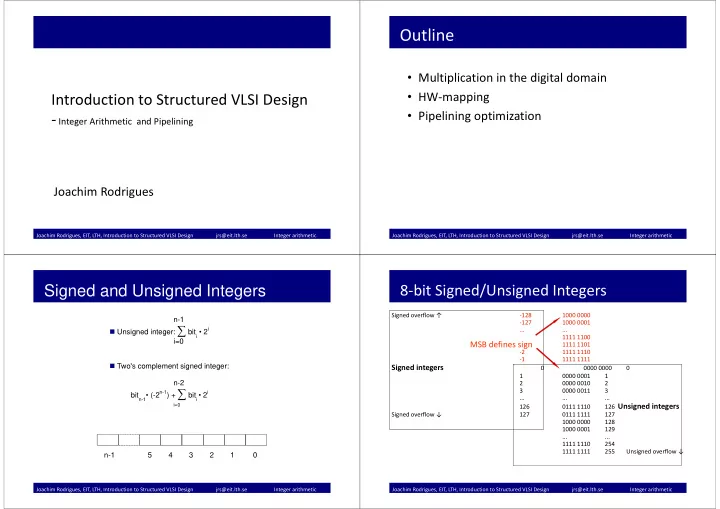

n-1 Unsigned integer: ∑ biti • 2i i=0 Two's complement signed integer: n-2 bitn-1• (-2n-1) + ∑ biti • 2i

i=0

n-1 5 4 3 2 1 0

Signed and Unsigned Integers

Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se Integer arithmetic

Signed overflow ↑ ‐128 1000 0000 ‐127 1000 0001 ... ... 1111 1100 1111 1101 ‐2 1111 1110 ‐1 1111 1111

Signed integers

0000 0000 1 0000 0001 1 2 0000 0010 2 3 0000 0011 3 ... ... ... 126 0111 1110 126 Unsigned integers Signed overflow ↓ 127 0111 1111 127 1000 0000 128 1000 0001 129 ... ... 1111 1110 254 1111 1111 255 Unsigned overflow ↓

8‐bit Signed/Unsigned Integers

MSB defines sign