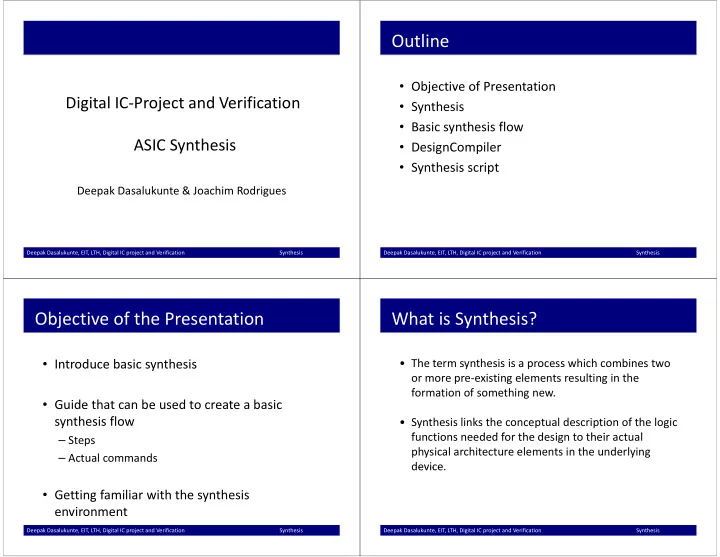

Digital IC‐Project and Verification ASIC Synthesis

Deepak Dasalukunte & Joachim Rodrigues Deepak Dasalukunte & Joachim Rodrigues

Deepak Dasalukunte, EIT, LTH, Digital IC project and Verification Synthesis

Outline

- Objective of Presentation

Objective of Presentation

- Synthesis

i h i fl

- Basic synthesis flow

- DesignCompiler

- Synthesis script

Deepak Dasalukunte, EIT, LTH, Digital IC project and Verification Synthesis

Objective of the Presentation

- Introduce basic synthesis

Introduce basic synthesis G id h b d b i

- Guide that can be used to create a basic

synthesis flow

– Steps – Actual commands

- Getting familiar with the synthesis

Deepak Dasalukunte, EIT, LTH, Digital IC project and Verification Synthesis

g y environment

What is Synthesis?

- The term synthesis is a process which combines two

The term synthesis is a process which combines two

- r more pre‐existing elements resulting in the

formation of something new.

- Synthesis links the conceptual description of the logic

f ti d d f th d i t th i t l functions needed for the design to their actual physical architecture elements in the underlying device device.

Deepak Dasalukunte, EIT, LTH, Digital IC project and Verification Synthesis