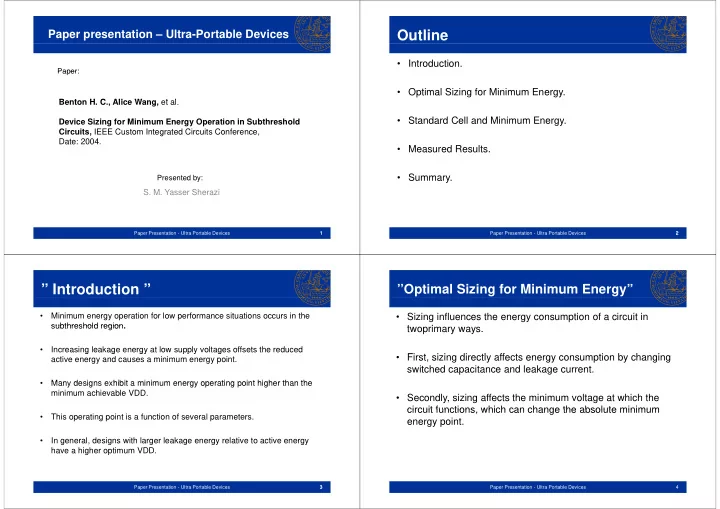

Paper presentation – Ultra-Portable Devices

Paper: Paper:

B t H C Ali W t l Benton H. C., Alice Wang, et al. Device Sizing for Minimum Energy Operation in Subthreshold Circuits, IEEE Custom Integrated Circuits Conference, Date: 2004.

Presented by:

- S. M. Yasser Sherazi

1 Paper Presentation - Ultra Portable Devices

Outline

- Introduction.

- Optimal Sizing for Minimum Energy.

- Standard Cell and Minimum Energy.

- Measured Results.

- Summary.

2 2 Paper Presentation - Ultra Portable Devices

” Introduction ”

- Minimum energy operation for low performance situations occurs in the

subthreshold region subthreshold region.

- Increasing leakage energy at low supply voltages offsets the reduced

g g gy pp y g active energy and causes a minimum energy point. Man designs e hibit a minim m energ operating point higher than the

- Many designs exhibit a minimum energy operating point higher than the

minimum achievable VDD.

- This operating point is a function of several parameters.

- In general, designs with larger leakage energy relative to active energy

have a higher optimum VDD.

3 Paper Presentation - Ultra Portable Devices

’’Optimal Sizing for Minimum Energy’’

- Sizing influences the energy consumption of a circuit in

t i twoprimary ways. Fi t i i di tl ff t ti b h i

- First, sizing directly affects energy consumption by changing

switched capacitance and leakage current.

- Secondly, sizing affects the minimum voltage at which the

circuit functions which can change the absolute minimum circuit functions, which can change the absolute minimum energy point.

4 Paper Presentation - Ultra Portable Devices