SLIDE 1

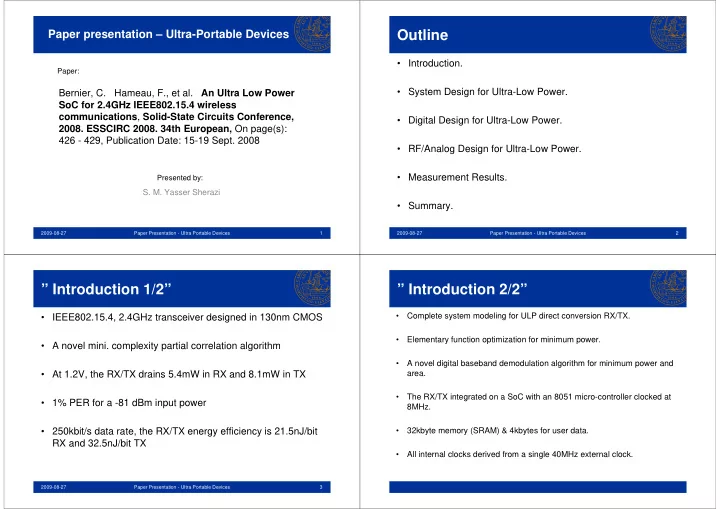

Paper presentation – Ultra-Portable Devices

Paper: Presented by:

Bernier, C. Hameau, F., et al. An Ultra Low Power SoC for 2.4GHz IEEE802.15.4 wireless communications, Solid-State Circuits Conference,

- 2008. ESSCIRC 2008. 34th European, On page(s):

426 - 429, Publication Date: 15-19 Sept. 2008

- S. M. Yasser Sherazi

2009-08-27 1 Paper Presentation - Ultra Portable Devices

Outline

- Introduction.

- System Design for Ultra-Low Power.

- Digital Design for Ultra-Low Power.

- RF/Analog Design for Ultra-Low Power.

- Measurement Results.

- Summary.

2009-08-27 2 Paper Presentation - Ultra Portable Devices

” Introduction 1/2”

- IEEE802.15.4, 2.4GHz transceiver designed in 130nm CMOS

- A novel mini. complexity partial correlation algorithm

- At 1.2V, the RX/TX drains 5.4mW in RX and 8.1mW in TX

- 1% PER for a -81 dBm input power

- 250kbit/s data rate, the RX/TX energy efficiency is 21.5nJ/bit

RX and 32.5nJ/bit TX

2009-08-27 3 Paper Presentation - Ultra Portable Devices

” Introduction 2/2”

- Complete system modeling for ULP direct conversion RX/TX.

- Elementary function optimization for minimum power.

- A novel digital baseband demodulation algorithm for minimum power and

area.

- The RX/TX integrated on a SoC with an 8051 micro-controller clocked at

8MHz.

- 32kbyte memory (SRAM) & 4kbytes for user data.

- All internal clocks derived from a single 40MHz external clock.