SLIDE 6 6

10/14/2005 Caltech 31

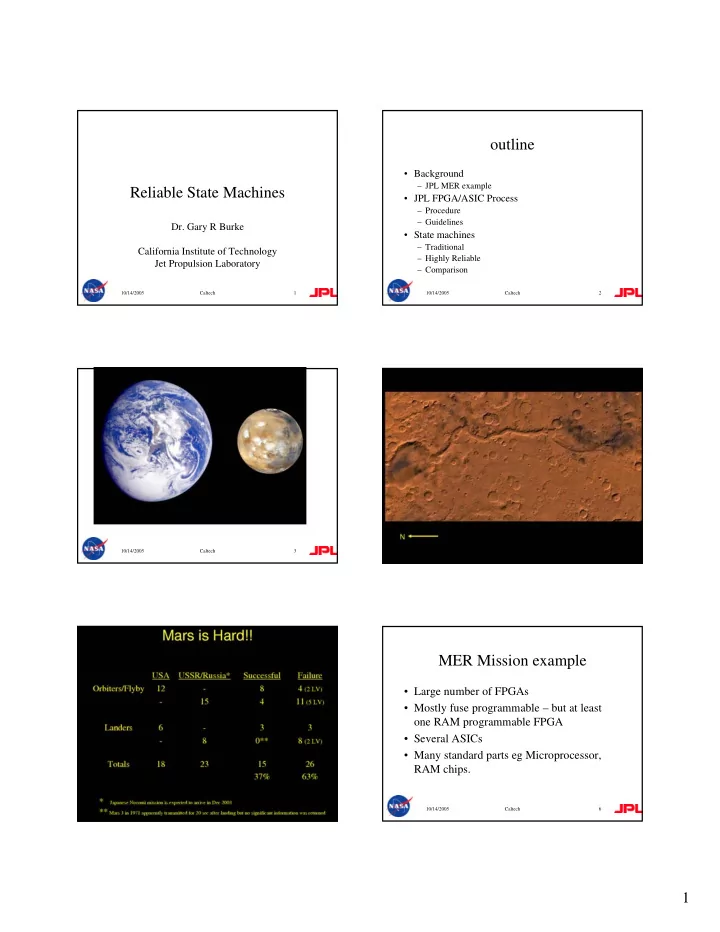

Eight Bit State Encoding

8 Bit State Encoding 3 8 4 6 15 20 22 15 5.6 5.1 7.5 8.5 5 10 15 20 25 Binary One Hot Hamming 2 Hamming 3 # of Slice Flip Flops # of Four Input LUTs Clock Period (ns)

10/14/2005 Caltech 32

Twelve Bit State Encoding

12 Bit State Encoding

4 12 5 7 25 31 41 55 7.7 5.8 8.0 9.5 10 20 30 40 50 60 Binary States One Hot Hamming 2 Hamming 3 # of Slice Flip Flops # of Four Input LUTs Clock Period (ns)

10/14/2005 Caltech 33

Sixteen Bit State Encoding

16 Bit State Encoding

4 16 5 7 38 41 49 71 8.2 6.7 8.5 9.8 10 20 30 40 50 60 70 80 Binary One Hot Hamming 2 Hamming 3 # of Slice Flip Flops # of Four Input LUTs Clock Period (ns)

10/14/2005 Caltech 34

Twenty-Four Bit State Encoding

24 Bit State Encoding

5 24 6 9 50 91 9.1 6.7 10.9 11.3 63 84 10 20 30 40 50 60 70 80 90 100 Binary One Hot Hamming 2 Hamming 3 # of Slice Flip Flops # of Four Input LUTs Clock Period (ns)

10/14/2005 Caltech 35

Thirty-Two Bit State Encoding

32 Bit State Encoding

5 6 9 96 107 137 14.6 11.5 12.0 32 237 10.6 50 100 150 200 250 Binary One Hot Hamming 2 Hamming 3 # of Slice Flip Flops # of Four Input LUTs Clock Period (ns)

10/14/2005 Caltech 36

Fault Injection Test

- A test circuit is generated with an example of each

state machine executing the same task, plus a reference state machine

- The task chosen requires a16-state state machine,

to detect a 16-bit pattern in a serial input stream

- An error generator injects faults into all state

machines except the reference state machine