1

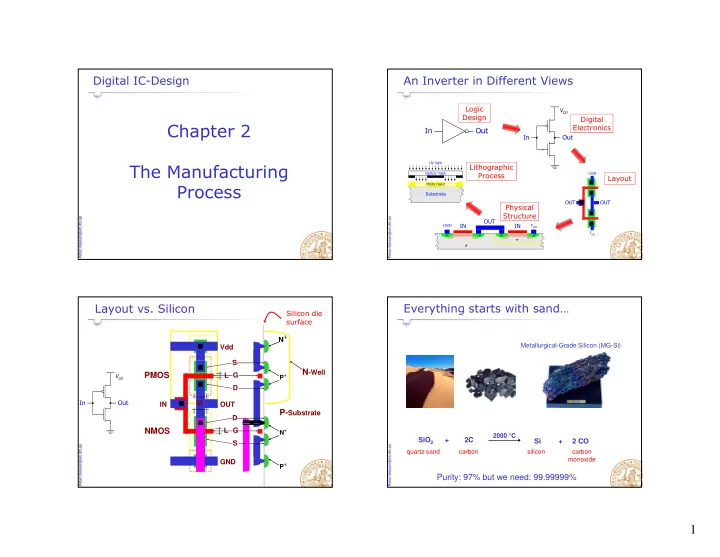

Chapter 2

Digital IC-Design

Chapter 2 The Manufacturing Process Process

Logic Design

An Inverter in Different Views

Out In

VDD

Digital Electronics Out In

Out In

Substrate

UV light Photo resist Optical mask

Lithographic Process

GND

Layout

p-

OUT

VDD

n+ n+ p+ p+ n-

GND

IN IN

Physical Structure

OUT

VDD

OUT

Layout vs. Silicon

N+ Vdd S Silicon die surface

N-Well P-Substrate

P+

PMOS

W L IN OUT S G D D

Out

VDD

In P+ N+

NMOS

L GND G S

Everything starts with sand…

Metallurgical-Grade Silicon (MG-Si)

SiO2 + 2C

2000 °C

Si + 2 CO

quartz sand carbon carbon monoxide silicon

Purity: 97% but we need: 99.99999%