4 1 3 2 Instruction ALU Registers Memory Fetch and Decode - PowerPoint PPT Presentation

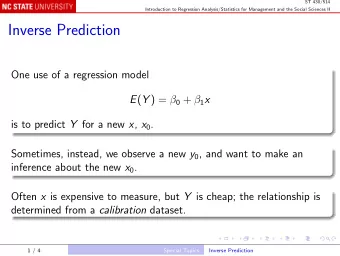

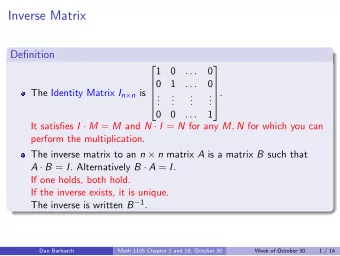

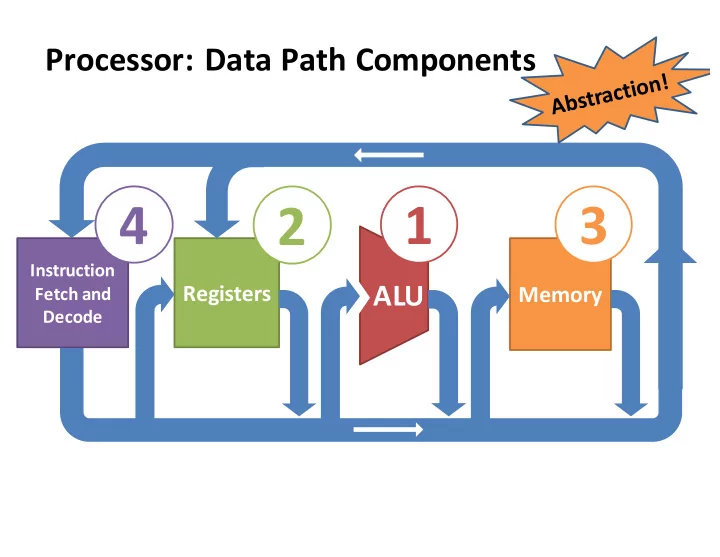

Processor: Data Path Components 4 1 3 2 Instruction ALU Registers Memory Fetch and Decode Building Blocks Processor datapath Microarchitecture Instruction Decoder Memory Arithmetic Logic Unit Adders Registers Multiplexers

Processor: Data Path Components 4 1 3 2 Instruction ALU Registers Memory Fetch and Decode

Building Blocks Processor datapath Microarchitecture Instruction Decoder Memory Arithmetic Logic Unit Adders Registers Multiplexers Demultiplexers Flip-Flops Digital Logic Encoders Latches Decoders Gates Devices (transistors, etc.)

1 Arithmetic Logic Unit (ALU) a few bits Condition Codes (sign, overflow, carry-out, zero) word Operand A ALU words Result Operand B Operation a few bits Hardware unit for arithmetic and bitwise operations.

ex 1-bit ALU for bitwise operations Build an n-bit ALU from n 1-bit ALUs. Each bit i in the result is computed from the corresponding bit i in the two inputs. Op A B Result 0 0 0 Operation 0 0 1 A 0 1 0 0 MUX 0 1 1 Result 1 0 0 B 1 1 0 1 1 1 0 1 1 1

ex 1-bit adder Build an n-bit adder from n 1-bit adders. Each bit i in the result is computed from the corresponding bit i in the two inputs and the carry out of bit i-1 . A B Carry in Carry out Sum Carry in 0 0 0 0 0 1 + A 0 1 0 Sum 0 1 1 look inside B during lab 1 0 0 1 0 1 Carry out 1 1 0 1 1 1

Carry in n-bit ripple-carry adder A 0 + Sum 0 B 0 A 1 + Sum 1 B 1 A 2 + Sum 2 B 2 … A n-1 + Sum n-1 B n-1 Carry out There are faster, more complicated ways too…

1-bit ALU Operation Carry in 2 a 0 MUX Result 1 Sum + 2 b Carry out

Carry in 2 Operation n-bit ALU A 0 0 Result 0 MUX with ripple carry 1 Sum + B 0 2 A 1 0 Result 1 MUX 1 Sum + B 1 2 .... … A n-1 0 Result n-1 MUX 1 Sum + B n-1 2 Carry out

Adding subtraction Operation Carry in Invert B 2 A 0 MUX Result 1 Sum + B 2 0 MUX 1 Carry out Different than in SCO book.

ALU Condition Codes (x86) Extra ALU outputs describing properties of result. Zero Flag: 1 if result is 00...0 else 0 Sign Flag: sign bit of result Carry Flag: 1 if unsigned overflow else 0 carry-out bit of result Overflow Flag: 1 if signed overflow else 0

Compute NAND, NOR, NOT A, ex Set inputs as needed. Invert A Operation Invert B Carry in 2 A 0 0 MUX 1 MUX Result 1 Sum + B 2 0 MUX 1 Carry out

Compute <, ==? Detect overflow? ex Set inputs as needed, add minimal logic for overflow. Invert A Operation Invert B Carry in 2 A 0 0 MUX 1 MUX Result 1 Sum + B 2 0 MUX 1 Carry out

Negate B Operation Invert A 2 n-bit ALU A 0 0 0 1 Result 0 MUX 1 + B 0 0 2 1 A 1 0 0 1 Result 1 MUX 1 + B 1 0 2 1 .... .... .... … A n-1 0 0 1 Result n-1 MUX 1 + B n-1 0 2 1 Carry out

Controlling the ALU Condition Codes ALU control lines Function 0000 AND Operand A 0001 OR ALU Result 0010 add Operand B 0110 subtract 1100 NOR Control Lines Invert A Operation ID Negate B

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.