1

Core (IP)-Based Design – Lecture 5&6 in Hardware/Software Co-Design 2001

Tomas Henriksson Computer Engineering

- Dept. of EE

Linköpings universitet

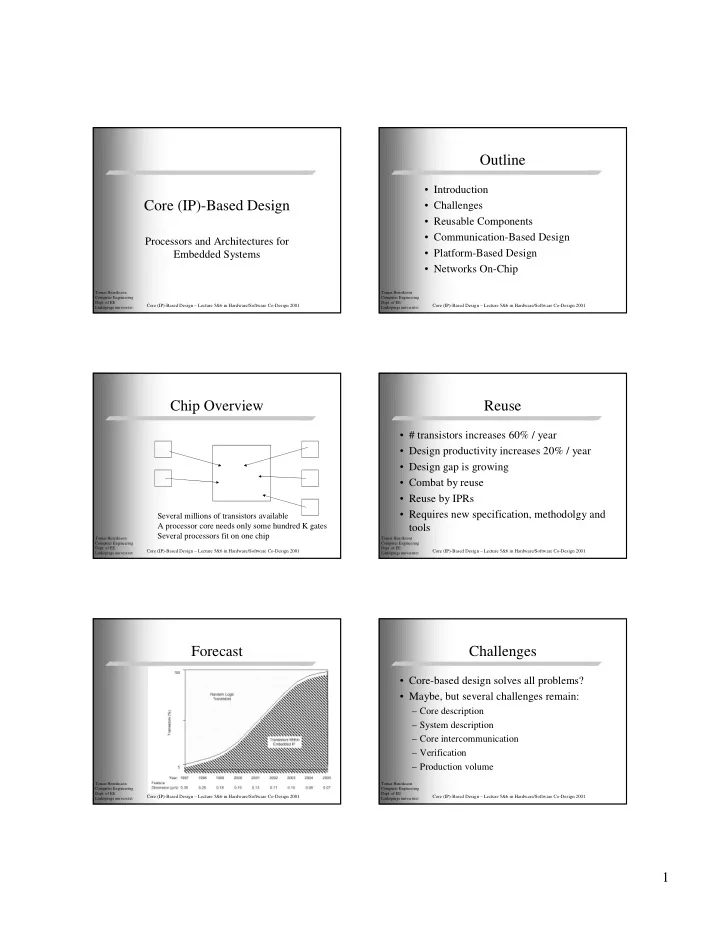

Core (IP)-Based Design

Processors and Architectures for Embedded Systems

Core (IP)-Based Design – Lecture 5&6 in Hardware/Software Co-Design 2001

Tomas Henriksson Computer Engineering

- Dept. of EE

Linköpings universitet

Outline

- Introduction

- Challenges

- Reusable Components

- Communication-Based Design

- Platform-Based Design

- Networks On-Chip

Core (IP)-Based Design – Lecture 5&6 in Hardware/Software Co-Design 2001

Tomas Henriksson Computer Engineering

- Dept. of EE

Linköpings universitet

Chip Overview

Several millions of transistors available A processor core needs only some hundred K gates Several processors fit on one chip

Core (IP)-Based Design – Lecture 5&6 in Hardware/Software Co-Design 2001

Tomas Henriksson Computer Engineering

- Dept. of EE

Linköpings universitet

Reuse

- # transistors increases 60% / year

- Design productivity increases 20% / year

- Design gap is growing

- Combat by reuse

- Reuse by IPRs

- Requires new specification, methodolgy and

tools

Core (IP)-Based Design – Lecture 5&6 in Hardware/Software Co-Design 2001

Tomas Henriksson Computer Engineering

- Dept. of EE

Linköpings universitet

Forecast

Core (IP)-Based Design – Lecture 5&6 in Hardware/Software Co-Design 2001

Tomas Henriksson Computer Engineering

- Dept. of EE

Linköpings universitet

Challenges

- Core-based design solves all problems?

- Maybe, but several challenges remain: