- 07 Memory

07.02 Non-volatile memory chips

- NAND and NOR memories

- Floating gate transistors

- FLASH memories

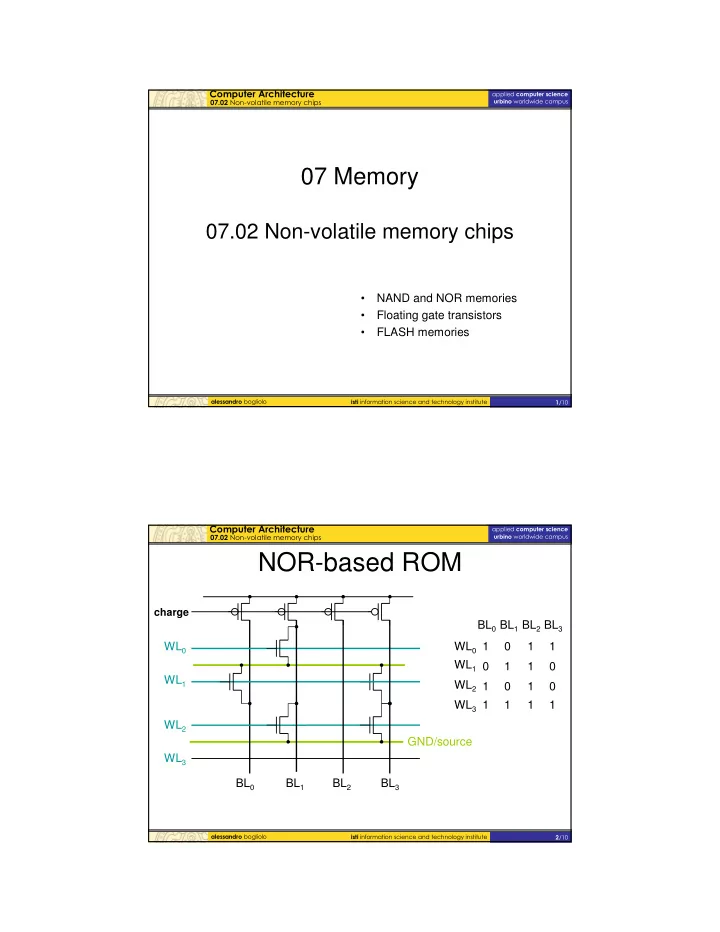

- NOR-based ROM

GND/source WL0 WL1 WL2 WL3 BL0 BL1 BL2 BL3

charge

WL0 WL1 WL2 WL3 BL0 BL1 BL2 BL3 1 1 1 1 1 1 1 1 1 1 1

NOR-based ROM charge BL 0 BL 1 BL 2 BL 3 WL 0 WL 0 1 0 1 1 WL 1 - - PDF document

GND/source WL0 WL1 WL2 WL3 BL0 BL1 BL2 BL3

charge

WL0 WL1 WL2 WL3 BL0 BL1 BL2 BL3 1 1 1 1 1 1 1 1 1 1 1

WL0 WL1 WL2 WL3 BL0 BL1 BL2 BL3

charge

WL0 WL1 WL2 WL3 BL0 BL1 BL2 BL3 1 1 1 1 1

Control gate Floating gate n+ source n+ drain p-substrate bulk

(Fowler-Nordheim tunneling) Programming (hot-electron injection)

(F-N tunneling)

VGS

FG FG T

C Q V ∆ − = ∆

Without charge in the FG With negative charge in the FG 1 1 Works like a transistor Works like an open line With positive charge in the FG 1 Works like a short circuit

http://www.m-sys.com/site/en-US/Corporate/Technology/NANDandNOR_Flash_Technologies.htm DiskOnChip NOR NAND

Capacity 8MB-1024MB 1MB-32MB 16MB-512MB XIP (code execution) XIP boot block Yes None Fast erase (3 msec) VERY SLOW erase (5 sec) Fast erase (3 msec) Fast write Slow write Fast write Fast read Fast read Fast read Extremely high: Standard: Low: Built-in EDC/ECC solves bit-flipping. Bit-flipping issues reported Requires 1-4 bit EDC/ECC due to bit-flipping issue. Bad block managed by TrueFFS. Less than 10% the life span of NAND. Requires bad-block management. Erase Cycles 100,000 - 1,000,000 10,000 - 100,000 100,000 - 1,000,000 Interface SRAM/NOR-like Full memory interface I/O only Access Method RND on code area, SEQ on data area. Random Sequential Ideal Usage Both data and code storage in any application that requires a file system. Code storage - limited capacity due to price in high capacity. May save limited data as well. Data storage only - due to complicated flash management. Code will usually not be stored in raw NAND flash. Examples Smartphones Simple home appliances PC Cards PDAs Embedded designs Compact Flash Point-Of-Sale Workstations Low-end set top boxes Secure Digital SCB/IPC Low-end mobile handsets MP3 players Digital Gateways PC BIOS chips Digital Cameras Telecom Equipment Set-Top Boxes Thin Clients Price Low High Low Reliability Performance